Broadcom’s Strategic AI Infrastructure Play

While GPUs dominate AI infrastructure discussions, the interconnect fabrics enabling multi-trillion-parameter models are equally crucial. Broadcom has been quietly developing technologies across various domains, from scale-out Ethernet fabrics to package-level interconnects. Unlike Nvidia, Broadcom operates as a merchant silicon company, selling chips and IP to multiple vendors, which could accelerate its market penetration.

The Scale of AI Networking

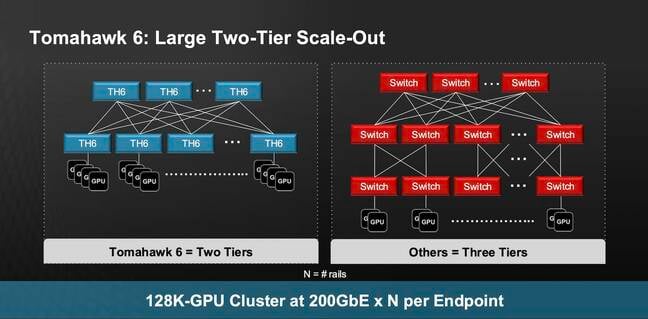

Connecting massive AI clusters requires substantial networking infrastructure. For instance, a 128,000-accelerator cluster might need over 5,000 switches just for the compute fabric. Broadcom has been addressing this demand with high-radix switches like the 102.4Tbps Tomahawk 6, which can support up to 128,000 GPUs with just 750 switches in a two-tier architecture.

Ethernet’s Role in Scale-Up Networks

Broadcom is positioning Ethernet as a viable solution for rack-scale architectures, competing with specialized interconnects like Nvidia’s NVLink or the emerging Ultra Accelerator Link (UALink). Intel is already using Ethernet for both scale-up and scale-out networks in its Gaudi systems, while AMD plans to tunnel UALink over Ethernet in its first-generation rack-scale systems.

Advancements in Co-Packaged Optics

Broadcom has been investing in co-packaged optics (CPO) technology, which integrates lasers, digital signal processors, and retimers onto the same package as the switch ASIC. The latest generation offers up to 200Gbps per lane of optical connectivity, with plans for 400Gbps lanes by 2028. This technology significantly reduces power consumption compared to traditional pluggable optics.

Optical Interconnects for Accelerators

To extend scale-up networks beyond a single rack, Broadcom is exploring optical interconnects directly on accelerators. The company has demonstrated a 6.4Tb/s optical Ethernet chiplet that can be co-packaged with GPUs, potentially supporting 512 GPUs as a single scale-up system.

Chiplet Architecture Innovations

Broadcom is also developing its 3.5D eXtreme Dimension System in Package (3.5D XDSiP) technology, a blueprint for building multi-die processors. This approach allows for higher die-to-die interconnect speeds and denser electrical interfaces between chiplets using hybrid copper bonding.

The first parts based on these designs are expected to enter production in 2026, potentially revolutionizing how AI chips are designed and interconnected.